## 片上网络的拓扑结构研究

#### 胡伟

(黄山学院 信息工程学院、安徽 黄山 245021)

摘 要:随着 SoC 体系结构设计复杂度的提高,传统的总线结构已成为 IP 核之间通信的瓶颈,新的设计方法片上网络(NoC)应运而生。在对 NoC 拓扑结构进行了分类的基础上,分析了各种网络拓扑的相关特性,结果表明这些拓扑结构都具有良好的可扩展性,文章还探讨了 NoC 拓扑结构的发展方向。

关键词:片上网络(NoC);片上系统(SoC);拓扑结构

中图分类号: TP302 文献标识码: A 文章编号: 1672-447X(2010)04-0083-04

#### 1 引 宮

随着半导体工艺技术步入纳米阶段,在单一芯片中集成上亿晶体管已经成为现实,片上系统(SoC)的发展已经进入极其迅速的时代。按照不同的片上互连方式,多核 SoC 可分为两大类,即传统的基于总线的互连和基于网络的互连。前者是现有 SoC 的扩展,通过多总线及层次化总线等技术使得片上集成更多的处理器核,从而实现高复杂度和高性能,而后者是近些年提出的崭新概念,即多处理器核之间采用分组路由的方式进行片内通信,从而克服了由总线互连所带来的各种瓶颈问题,这种片内通信方式称为片上网络 (Network on a Chip, NoC)。自从 NoC 概念在 2000 年第一次被提出,已经过 10 年的发展,已经进入技术逐步成熟的阶段。

#### 2 片上网络体系结构

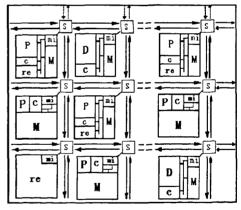

NoC 中允许存在任意类型的资源节点,典型的资源节点可以是带缓冲的嵌入式微处理器和 DSP 核、专用硬件资源、可重构硬件资源,或者是上述各种硬件的组合。图 1 显示了资源节点中可能包含的硬件资源。计算类的资源节点以微处理器核、DSP

核等形式存在,而存储类的资源节点则要求尽可能地分散,以避免访问数据时要跨越整个芯片。各种尺寸的 SRAIMS、DRAIMS、FLASFI 满足了不同的需求。

图 1 资源节点中包含各种类型的硬件资源

通讯节点是互连网络中的主要部分,其核心就是交换开关。如网络中的路由器,其主要作用是寻找出信息从起点到终点的最短最有效的路径。在数据传输中,有两种路由方式可供设计者选择:确定性路由(deterministic routing)和自适应路由(adaptive routing)但是对于 NoC 设计,自适应路由规则并不适合。这并不是考虑自适应路由中路由表的存在,而是由计算升级和维持信息的复杂度决定的。

收稿日期:2010-05-10

作者简介:胡 伟(1978-),安徽绩漠人,黄山学院信息工程学院讲师,项士,主要研究方向为嵌入式系统综合与测试、计算机控制。

#### 3 片上网络的拓扑结构

为了满足不同的性能和成本等需求,人们设计了很多不同的专用多处理器网络拓扑。MPSoC (Multi-Processor System-on-Chip)网络可以被分成直接网络和间接网络两类。在直接网络 MPSoC 中,节点处理器通过网络直接相互连接,每个节点执行数据流路由和仲裁。在间接网络 MPSoC 中,节点处理器通过一个或多个中间节点开关相连,开关节点执行路由和仲裁功能。间接网络也称为多阶段互连网络(Multistage Interconnect Networks,MIN)。

NOC 的拓扑结构有直接网络 Orthogonal 拓扑,立体连接循环(Cube-Connected-Cycle)拓扑、Octagon 拓扑等;间接网络拓扑 Crossbar Switch 结构、Fully-Connected 网络、Butterfly 拓扑等。

#### 3.1 直接网络拓扑

#### 3.1.1 Orthogonal 拓扑

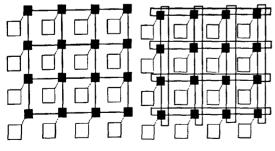

Orthogonal 拓扑网络中节点以 K-阵列 N-维 Mesh<sup>III</sup>或者 K-阵列 N-维 Torus<sup>III</sup>形式互连。如图 2 所示的就是一个 2-D Mesh 网格结构,从图中可以看到,每个资源节点和一个交换节点相连,而一个交换节点和 4 个相邻的交换节点相连,二维网格结构在带宽、时延等通信性能上并不是最优,但其结构简单、可重用性好、可扩展性强,因此成为研究最多的拓扑结构。Torus 网络结构在 Mesh 网格结构的基础上,将位于边缘的两个节点也连接了起来,如图 3 所示,环面网络结构的优点在于增强了位于边缘的节点之间的通讯,其缺点在于增加的边缘的节点之间的连线与其它连线有交叉,增加了布线的困难。Mesh 和 Torus 网络在并行计算平台中被广泛使用。

图 2 Mesh 网络

图 3 Torus 网络

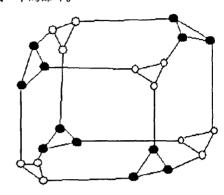

# 3.1.2 立方体连接循环拓扑 立方体连接循环拓扑是为了减少 Orthogonal

拓扑中每个节点的度而设计的。如图 4 所示,3-立 方结构的每个节点有 3 个度,而在 Mesh 和 Torus 网络中每个节点有 2n 个度,立方体互连周期拓扑 有一个层次化结构,在立方体的每个角上 3 个节点 形成一个局部环。

图 4 Octagon 网络

#### 3.1.3 Octagon 拓扑

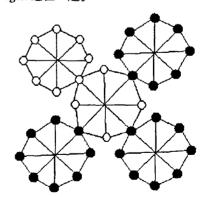

Octagon 网络是为网络处理器提出的一个片上通信结构。F.Kariml<sup>19</sup>等人在设计网络处理器时提出了一个如图 5 所示的八角形网络。这种结构中,8个处理器通过一个 Octagon 环和 3 个直径相连。任意两个处理器之间的延迟在局部环中不超过两个阶段,即通过一个中间节点,这个 Octagon 网络是可伸缩的。如果一个处理器作为桥节点,可以把更多的 Octagon 连在一起。

图 5 立方连接循环

#### 3.2 间接网络拓扑

#### 3.2.1 Crossbar Switch 结构

一个 N×N Crossbar 网络连接 N 个输入端口和 N 个输出端口。N 个输入端口的任意一个都可以和 任意一个输出端口通过对应的交叉点上的节点开 关相连。

图 6 Crossbar Switch 结构

#### 3.2.2 Fully-Connected 网络

一个 N×N 完全互连网络使用 MUXes 把每个输入聚合到输出,如图 7 所示。仲裁器控制着每个MUX,决定哪个输入指向哪个输出。

图 7 全连接 Switch 结构

与交叉网络相似,完全互连开关网络也常称为 Crossbar,在完全互连开关网络中,每个源-目的连 接有专门的数据路径。

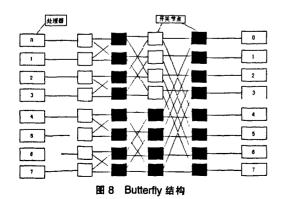

#### 3.2.3 Butterfly 拓扑

Butterfly 网络(如图 8)是一个间接网络结构。在 Butterfly 结构中,每个源到目的路由是用一个专门 的数据路径。任意两个处理器节点之间的延迟是一 样的,延迟时间由开关结构上的中间阶段数目决 定。

Butterfly 拓扑有很多不同的同构变体,如 Banyan Network,Batcher-Banyan Networks 等。

#### 3.2.4 Fat-tree 拓扑

树中的内节点是开关,叶子是处理器。除了根节点,每个内节点只与其父节点和若干个子节点相连。传统 K 叉树的主要问题是单个父节点尤其是根节点,容易成为通信瓶颈。Leiserson<sup>[4]</sup>于 1985 年提出的胖树,一个节点可拥有多个父节点,可以缓解此问题。因此,和 Butterfly 网络不同,胖树网络从源节点到目的节点提供了多个数据路径。胖树网络可被看作一个扩展的有多个根节点的 n—列树网络,网络延迟依赖于树的深度。

如图 9 所示,SPIN<sup>®</sup>网络是一个 4-列胖树拓扑的设计例子,每个处理器位于这个胖树的叶子节点上。被分割为分组的消息通过向上或向下遍历胖树网络在处理元件之间进行分组交换。一个分组被定义为一个 36 位的字。分组的头占用第一个字,头的一个字节代表目的地址,其他位用于作分组标志和路由信息。分组的有效负载时可变的,每个分组由一个尾部来终止,尾部不含数据,而是用来检错的。

图 9 SPIN 网络

#### 4 各种拓扑结构的对比

用来刻划一个拓扑结构的特征,并影响其性能的而又彼此关联的参数有:节点数,节点度,网络直径和链路数等。表1总结了一些典型规则拓扑的特性参数,这些参数常用来估计网络的复杂性、通信效率、成本等,是选择网络拓扑的重要依据。

表 1 典型规则拓扑的特性

| 网络拓扑     | 节点数                        | 节点度 | 网络直径                            | 链路數        |

|----------|----------------------------|-----|---------------------------------|------------|

| 2D-Mesh  | $\sqrt{N} \times \sqrt{N}$ | 4   | $2(\sqrt{N}-1)$ $2(N-\sqrt{N})$ |            |

| 2D-Torus | $\sqrt{N} \times \sqrt{N}$ | . 4 | $2\sqrt{N}/2$                   | 2 <i>N</i> |

| 立方体      | nN=2*                      | N   | N                               | nN/2       |

| Fat-Tree | N=2* 个 IP 核                | 3   | 2n-2                            | N-2        |

|          | N=2°↑IP核                   | 2   | n+2                             | (n-2)N     |

#### 5 结 论

NoC 解决了在 SoC 设计中存在的问题,是一种新的设计方法,它在信息吞吐量、延迟、能耗和芯片面积等方面做出了很大的改进。本文分析了 NoC 中常见的拓扑结构,指出了每种拓扑结构的主要特点,并综合地对几种典型拓扑从节点数,网络直径,节点度,链路数等方面进行了对比分析,这些拓扑结构都具有良好的可扩展性。

未来 NoC 拓扑结构的主要发展方向是:

- 1.增强系统的可测试性和可靠性,降低设计的 风险:

- 2.研究 Noc 模拟工具,降低设计成本,提高设计效率;

- 3.设计低复杂度的拓扑结构,减小芯片面积;

- 4.研究 NoC 降低功耗,提高系统性能。

同时,NoC 涉及了从物理实现到体系结构,到操作系统,到应用的各个层次,也就需要对其各个层面进行研究。

#### 参考文献:

- [1]M.Forsell, A scalable high-performance computing solution for networks on chips[J].IEEE Micro, 2002,22(5):46-55.

- [2]WJ Dally,B Towles,Route Packets,Not Wires: On -Chip Interconnection Networks [J]. DAC 2001, IEEE, 2001,18 (6):684-689.

- [3]F.Karim,A.Nguyen,S.Dey,R.Rao.On -chip communication architecture for OC -768 network processors [J].

Proceedings of 38th Design Automation Conference,June 2001,25(6):.678-683.

- [4]LEISERSON C E. Fat -trees: Universal networks for hardware-effi-cient supercomputing [J]. IEEE Transactions on Computers, 1985,34(10): 892-901.

- [5]ADRIAHANTENAINA A, CHARLERY H, GREINER A, et al.SPIN: A scalable, packet switched, on -chipmicro network [CJ/Proceedings of Design, Automation and Test in Europe Conferenceand Exhibition. Washington, DC, USA: IEEE ComputerSociety, 2003: 70-73.

责任编辑:胡德明

## Research on the Topology Structure of Network-on-Chip

Hu Wei

(School of Information Engineering, Huangshan University, Huangshan 245021, China)

Abstract: With the increasing complexity of SoC structure design, the traditional bus structure has become the bottleneck of communication among IP blocks, thus a new design method for network-on-chip (NoC) came into being. On the basis of a classification for NoC topology structures, each specific topology was discussed in details. The results showed that the topology structures have good scalability. At the end of the paper, the future research direction of NoC topology structure was presented.

Key words: Network-on-Chip (NoC); System-on-Chip (SoC); topology structure

### 片上网络的拓扑结构研究

作者: 胡伟, Hu Wei

作者单位: 黄山学院, 信息工程学院, 安徽, 黄山, 245021

刊名: 黄山学院学报

英文刊名: JOURNAL OF HUANGSHAN UNIVERSITY

年, 卷(期): 2010, 12(5)

被引用次数: 0次

#### 参考文献(5条)

- 1. M. Forsell A scalable high-performance computing solution for networks on chips 2002(5)

- 2. WJ Dally. B Towles. Route Packets Not Wires: On-Chip Interconnection Networks 2001(6)

- 3. F. Karim. A. Nguyen. S. Dey. R. Rao On-chip communication architecture for OC-768 network processors 2001

- 4. LEISERSON C E Fat-trees: Universal networks for hardware-efficient supercomputing 1985(10)

- 5. ADRIAHANTENAINA A. CHARLERY H. GREINER A SPIN: A scalable, packet switched, on-chipmicronetwork 2003

#### 相似文献(10条)

1. 期刊论文 陈庚生. 陈亦欧. 胡剑浩. CHEN Geng-sheng. CHEN Yi-ou. HU Jian-hao 用于NoC映射的EDA工具设计 -中国集成电路2010, 19(1)

片上网络(NoC)作为解决片上系统(SoC)复杂通信问题的新的范例,受到了工业界和学术界的广泛重视.为了保证实时任务在片上网络上的高效运行,从任务到网络拓扑的映射问题成为NoC研究中的关键问题之一.为了得到各种条件下的不同映射结果和性能曲线,本文设计了一种通用的NoC映射EDA工具.该工具基于Matlab的GUI设计方法,具有界面友好、可重配置性、运行速度快、自动导出并存储仿真结果等特点.

2. 会议论文 葛芬. 吴宁 基于OPNET的片上网络设计仿真和性能分析 2008

片上网络(NoC)的提出是复杂片上系统(SoC)设计中全局互连问题的解决方案。为了获得最佳性能,需根据不同的应用选择NoC的设计参数。本文在高层次设计仿真环境0PNET 中对NoC建模和仿真,通过改变网络拓扑结构(二维网格、胖树和蝶形胖树)和交换技术(虫孔交换和虚跨步交换)对NoC体系结构的各种配置进行研究,并在不同的网络注入率和传输模式下仿真。论文根据延时和吞吐量比较分析仿真结果,结果可作为NoC设计者选择参数以获得NoC最佳性能的准则。

3. 期刊论文 宋朝晖. <u>马光胜</u>. 宋大雷. <u>SONG Zhao-hui</u>. <u>MA Guang-sheng</u>. <u>SONG Da-lei</u> <u>一种新的基于NoC的死锁检测算</u>

#### 法 -微电子学与计算机2009, 26(3)

为了适应实时片上系统SoC设计和片上网络NoC服务质量保证的可预测性需求,确保NOc高质量服务于实时系统,提出了一种新的基于NoC的死锁检测算法和它的硬件实现. 该算法用简单布尔表示请求、授权,且无活动,从而使其硬件实现更容易,操作更快,并证吸了该算法的正确性及其硬件实现的运行时间复杂性为0(min(m,n)),这里的m为资源数目,n是进程数.

4. 期刊论文 徐成. <u>陶海洋.</u> 刘彦. 龙榜. 王立东. XU Cheng. TAO Hai-yang. LIU Yan. LONG Bang. WANG Li-dong 延迟优化的片上网络低功耗映射 -计算机应用研究2009, 26 (10)

片上网络(NoC)是解决传统基于总线的片上系统(SoC)所面临的功耗、延迟、同步和信号完整性等挑战的有效解决方案. 功耗和延迟是NoC设计中的重要约束和性能指标,在设计的各个阶段都存在着优化空间. 基于蚁群优化算法, 通过通信链路上并发通信事件的均匀分布来降低NoC映射阶段的功耗和延迟. 仿真实验表明, 与链路通信量负载均衡的方法相比, 该方案能进一步在拓扑映射阶段优化功耗和延迟.

#### 5. 学位论文 丁帅 片上网络通信节点的研究与设计 2009

随着集成电路制造工艺技术的进步,片上系统SoC在设计过程中遇到了通信能力难以满足系统需求、全局时钟难以同步等问题,制约了集成在单一芯片上IP核的规模和数量。片上网络NoC采用基于包交换的通信方式和全局异步局部同步技术,将从体系结构上解决片上系统设计遇到的问题。本课题的主要工作是研究适用于二维网格拓扑结构的通信节点,在Synopsys公司的EDA环境下使用Verilog语言进行设计、仿真,并由该通信节点组成4×4的片上通信阿尔通信可信,这个通信节点的功能验证与性能分析。课题研究工作是构建片上网络模型的基础,可以为体系结构的制定、网络的构建等问题提供有效的参考。《br》

论文首先讨论了网络层和传输层的协议和关键技术,在此基础上,给出了通信节点的设计方案,对路由单元进行功能定义和模块划分。根据片上网络在性能、面积和功耗等方面的约束,在通信节点设计中,采用虚拟通道技术减小通道的阻塞概率,避免死锁的发生;在虚通道中加入虫孔通路以减少缓存的使用,降低系统的开销;采用双乒乓缓冲操作增加并行传输能力,提高链路带宽;选择OCP协议作为适配单元的核接口协议,提升片上网络的可扩展性。论文对所做设计工作在4×4的片上网络仿真平台上进行了验证,得到路由单元在工作频率、面积、功耗、传输延时以及链路带宽方面的性能指标,并给出了通信节点面积和传输延时方面的性能预测,通过性能分析给出了通信节点设计的优化策略。

6. 期刊论文 唐杉. 徐强. 丁炜. TANG Shan. XU Qiang. DING Wei 基于NoC的SoC中实时跟踪数据的传输 -计算机工程 2008, 34(15)

片上网络(NoC)技术使片上系统(SoC)的通信机制发生了根本改变,直接影响了SoC中处理器内核的实时跟踪技术.该文以ARM Coresight构架的实时跟踪机制为参考,分析了在NoC环境中实现实时跟踪数据传输的难点,提出相应的解决方案.通过对实验系统的仿真,验证了其中的关键技术.

#### 7. 学位论文 杨玲钊 NoC低摆幅互连研究 2010

集成电路自发明以来一直追求的目标就是芯片的工作速度更快、功耗更低、集成密度更大。随着集成电路设计水平的提高和工艺的发展,基于总线结构的片上系统(SoC)已经不能满足应用对片上数据通信的要求了,因此基于网络计算技术概念的片上网络(NoC)被提出来并得到广泛的研究。但是研究发现互连线上产生的功耗和延迟依然是制约系统性能的重要因素之一,因此针对互连线的研究成为当前学术界一个研究的热点。〈br〉

互连线上产生的功耗和延迟与所传输的信号的摆幅有着紧密的联系,因此采用低摆幅信号技术可以有效降低互连上产生的功耗和延迟,通过大量文献的阅读和总结,本文者重分析了八种低摆幅电路各自的特点、优缺点以及适用条件,并且在SMICO. 13μm工艺模型库、互连线采用第四层金属、宽度、间距

和长度为分别为 $0.4\mu$ m $0.4\mu$ m

#### 8. 学位论文 段新明 面向NoC的无死锁路由算法的研究 2007

随着计算机技术的发展,很多研究领域不断地交叉和融合。在微电子技术领域,一些研究者提出使用并行计算机互连网络技术解决单一芯片上多个内核的集成问题,这一技术称为片上网络(NoC)技术。NoC是片上系统(SoC)的通讯子系统,它利用互连网络解决单一芯片上的多个内核之间的通讯问题,这提高了单一芯片系统的通讯性能,也带来了互连网络中的一个关键问题,即网络死锁的问题。出于网络资源利用率和硬件成本等方面的考虑,本文提出使用死锁避免的策略,即设计无死锁的路由算法解决NoC网络中的死锁问题。

NoC网络与并行计算机互连网络之间有很多不同的地方,互连网络中的无死锁路由算法不能直接应用于NoC网络中。这首先是因为很多NoC网络(例如特定应用NoC网络)具有独特的拓扑结构,这就要求NoC网络路由算法具有更低的路由限制以保持路由的连通性。其次,由于芯片成本和功耗方面的限制,这就要求NoC网络路由算法使用更低数量的虚拟通道。NoC技术是芯片制造业发展的必然趋势,因此有必要现在开展NoC网络无死锁路由的研究,储备相关的核心技术。

针对于目前提出的一些可扩展的NoC网络结构,分别提出统一的、低虚拟通道使用和低路由限制的无死锁路由方案是本论文研究和探索的主要内容。研究工作的创新点主要体现在以下五个方面:

一是将NoC网络分为以特定应用NoC为代表的不规则拓扑结构网络和以多核处理器NoC为代表的规则拓扑结构网络。其中不规则拓扑结构网络包括非正交不规则网络和正交不规则网络(例如不规则Mesh网络),规则拓扑结构网络包括正交网络、非正交网络和具有部分正交特征的网络(例如RDT网络)。

二是提出了基于通道类依赖图的新的无死锁路由判定定理,这一定理与Duato定理是等价的,也是无死锁路由的充要判定条件。由于通道类依赖图与网络规模无关,这一定理可以成为NoC网络无死链路由复法设计的有力工具。

三是提出了不規则Mesh网络绕行障碍路由算法。这一算法与不規则Mesh的規模和形状无关,能够在具有不同矩形障碍区域的不規则Mesh网络中保持路由的连通性,同时算法只需要将网络中每一个物理通道分为三个虚拟通道使用。而且通过对这一算法进行扩展,本文分别提出了自适应、最短路径和耐盐障的不规则Mesh网络绕行障碍路由算法。

四是提出了不规则Mesh网络组合路由算法。组合路由算法由两个子路由算法组成,并使用两个虚拟通道,即每个子路由算法分别使用一个虚拟通道。通过将部分节点设置为路由盲区,组合路由算法能够在不规则Mesh网络中保持路由的连通性。本文还提出了基于组合矩阵计算和带权无向图的优化算法,这一算法能够最小化组合路由算法的路由盲区。

五是提出了PRDT(2, 1) 网络二进制路由算法,这一路由算法基于二进制计算进行路由决策,其路由决策速度更快。而且当网络规模较小时,这一算法无需使用虚拟通道即可实现无死锁路由。此外,基于这一算法本文进一步提出了完全自适应的二进制路由算法。

论文的结构如下:

第1章主要描述了互连网络中死锁产生的原因和解决的策略,以及一些经典的无死锁路由理论。

第2章介绍了NoC技术的产生及其网络结构,并对NoC网络拓扑结构进行了分类。

第3章提出了基于通道类依赖图的无死锁路由充要判定定理,并对其进行了证明。

第4章研究了基于不规则Mesh网络的NoC无死锁路由算法,提出了确定性、自适应、最短路径、耐故障的绕行障碍路由算法以及组合路由算法。

第5章讨论了基于PRDT(2,1)网络的NoC无死锁路由算法,提出了确定性和自适应的二进制路由算法。第6章对研究工作进行讨论和总结。

#### 9. 期刊论文 谭耀东. 刘有耀. TAN Yao-dong. LIU You-yao NoC系统研究综述 -西安邮电学院学报2008, 13(1)

片上网络(NoC)是实现片上系统(SoC)互连的一种新的范例, 关键是为了解决SoC内部组件之间的通信调度等问题而提出来的, 受到了工业界和学术界的广泛重视. NoC研究涉及从系统建模到具体实现流程的一系列问题, 本文主要讨论NoC研究中的关键问题、解决方案、当前的研究成果以及展望.

#### 10. 学位论文 翟欣虎 基于非规则结构片上网络路由算法的研究 2009

随着计算机处理器向多核技术发展,如何提高核与核之间的通信效率是提高多核技术性能的关键问题之一。从上个世纪九十年代中期到本世纪初,半导体集成电路芯片制造工艺先后经历从单核片上系统(SoC),多核片上系统(MPSoC),到片上网络(NoC)的发展过程。NoC是目前多核芯片技术的最佳发展形态。单核的SoC计算能力不强,一般只用于控制,很难适应复杂的工程计算。而MPSoC传统的总线构架具有不可避免的扩展性不强,并行性差的缺点。随着在单一芯片上所集成内核数目的增加,总线构架的系统将遇到无法逾越的通信瓶颈。NoC实际是基于网络通信的MPSoC,它把计算机网络技术移植到芯片系统中来,用路由和报文交换技术代替传统的总线技术完成通信任务,是单芯片上更高层次更大规模的网络系统。NoC从体系结构上解决了SoC的总线结构所固有的扩展性差,通信效率低,以及功耗和面积较大的问题,代表着未来的发展方向。〈br〉

本文在介绍了NoC多种拓扑结构特点,以及常用路由算法的前提下,对NoC非规则结构中的分层结构以及准规则结构进行了研究分析。针对它们的特点,设计了新的兔死锁混合路由算法以及新的节点编址方式。同时提出了新的交换节点设计构想,并给出了有效的拥塞控制策略。仿真结果表明,当网络中数据流量变大时这两种非规则的网络比典型的规则二维网络具有更小的传输时延以及更大的吞吐量。

本文链接: http://d.wanfangdata.com.cn/Periodical\_hsxyxb201005027.aspx

授权使用: 黄山学院学报(qkhsxy), 授权号: 5227d56c-3275-4dd0-993e-9ebd00b9bf13

下载时间: 2011年4月6日